Sınırlı Alanlarda Düşük ESR İçin Kapasitör Yığma Tekniği

Platformumuzdaki en çok okunan ve popüler makaleleri görmek için Trendler bölümüne geçebilirsiniz.

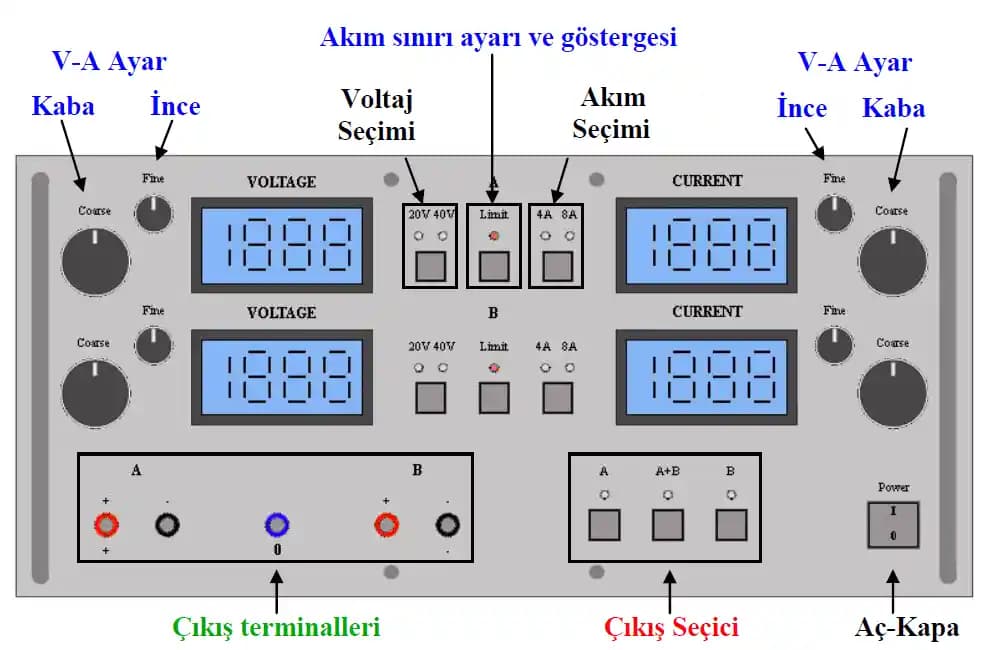

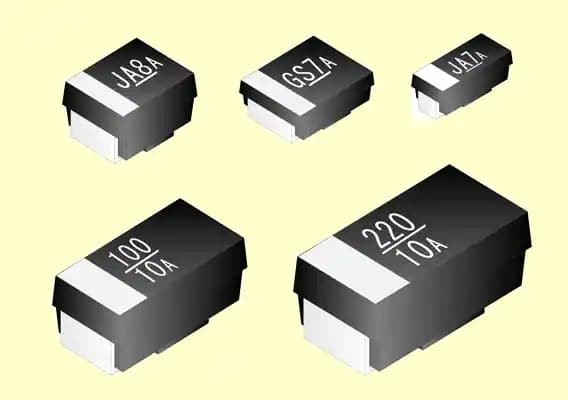

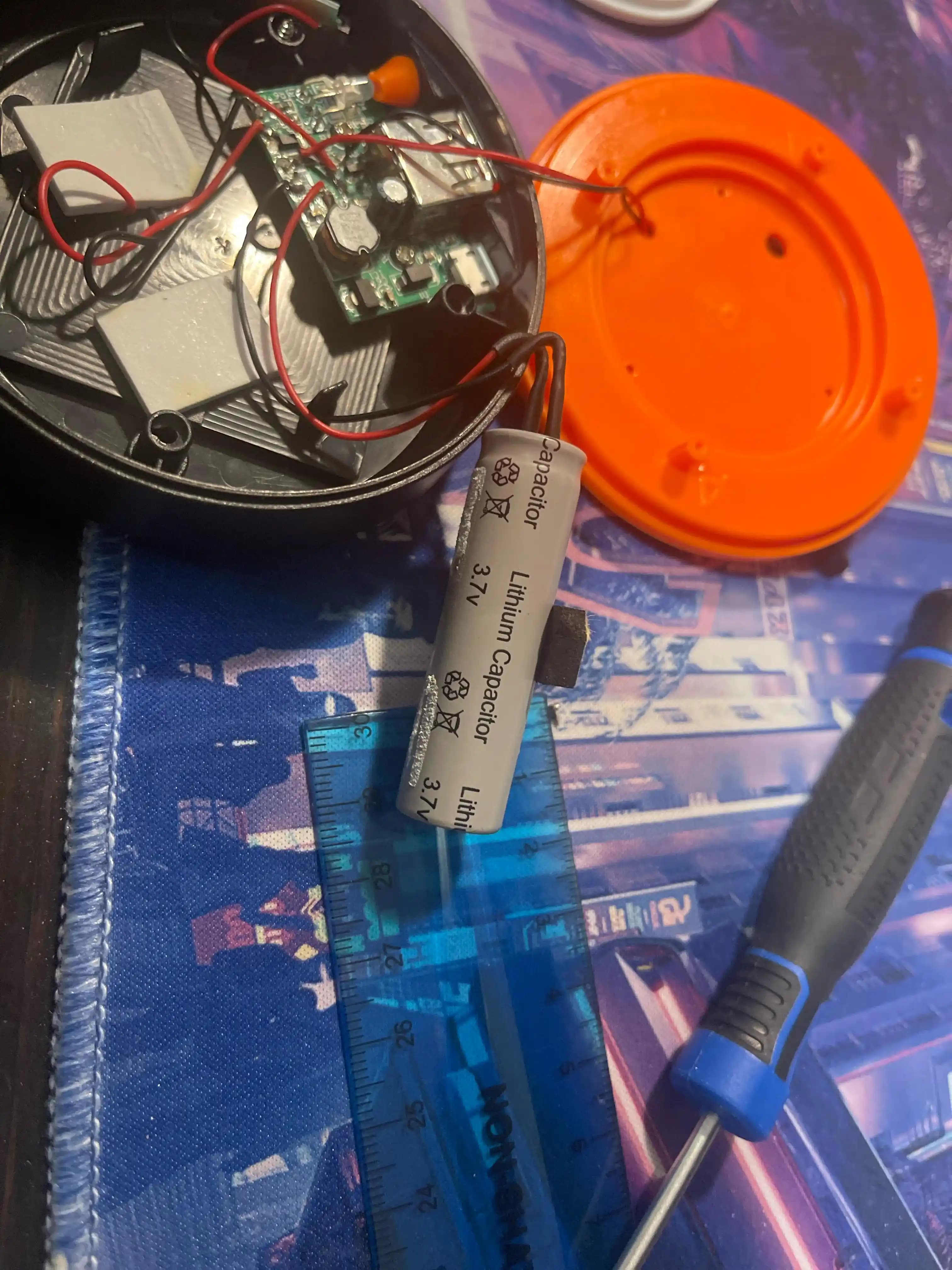

Elektronik devre tasarımında, özellikle yüksek performanslı ve kompakt sistemlerde, düşük ESR (eşdeğer seri direnç) değerine sahip kapasitörlerin kullanımı kritik öneme sahiptir. Ancak, devre kartında sınırlı alan olduğunda, istenilen kapasitans ve düşük ESR değerlerini sağlamak zorlaşır. Bu durumda, kapasitörlerin üst üste yığılması (stacking) yöntemi devreye girer.

Kapasitör Yığma Yöntemi ve Uygulamaları

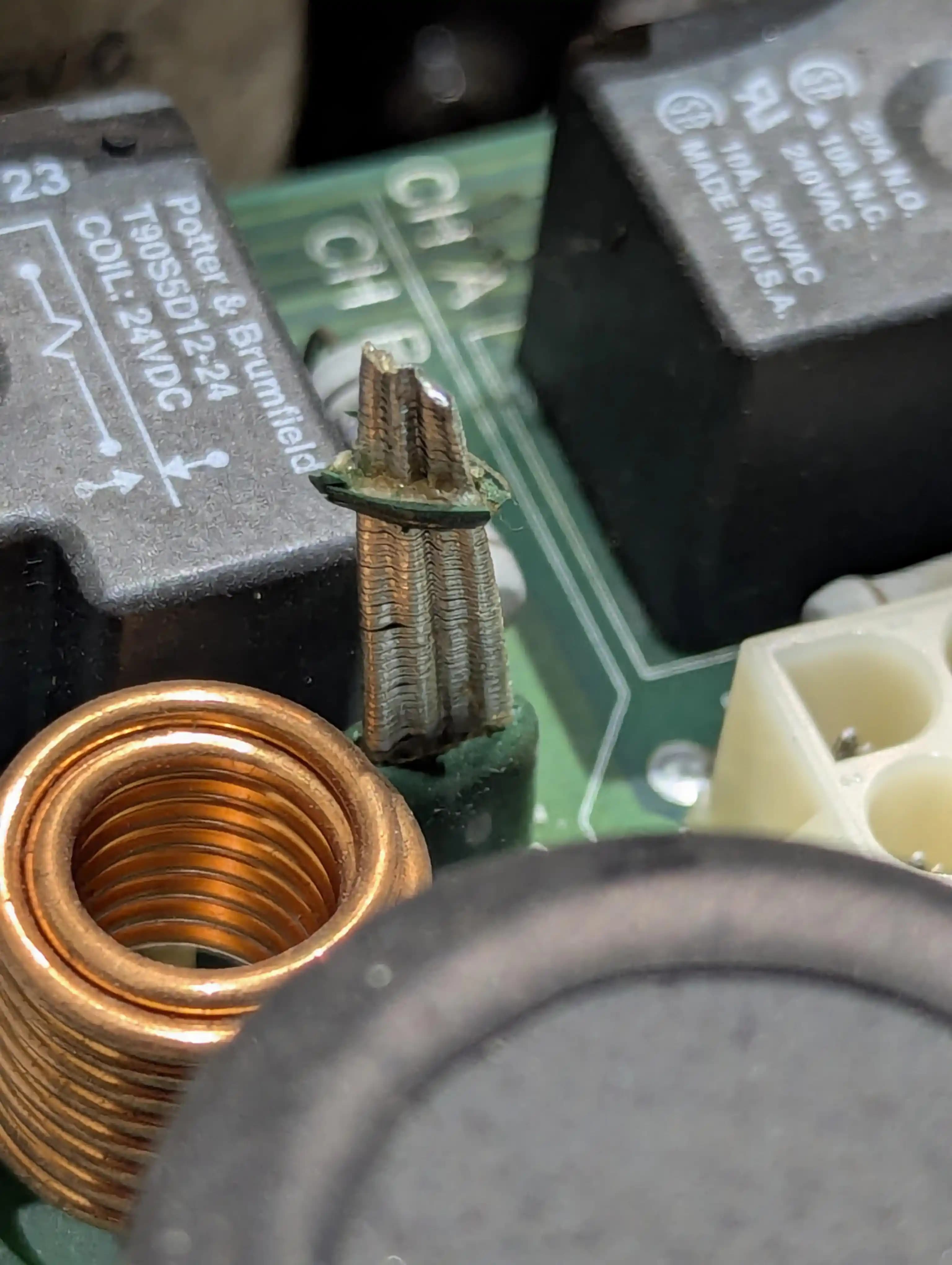

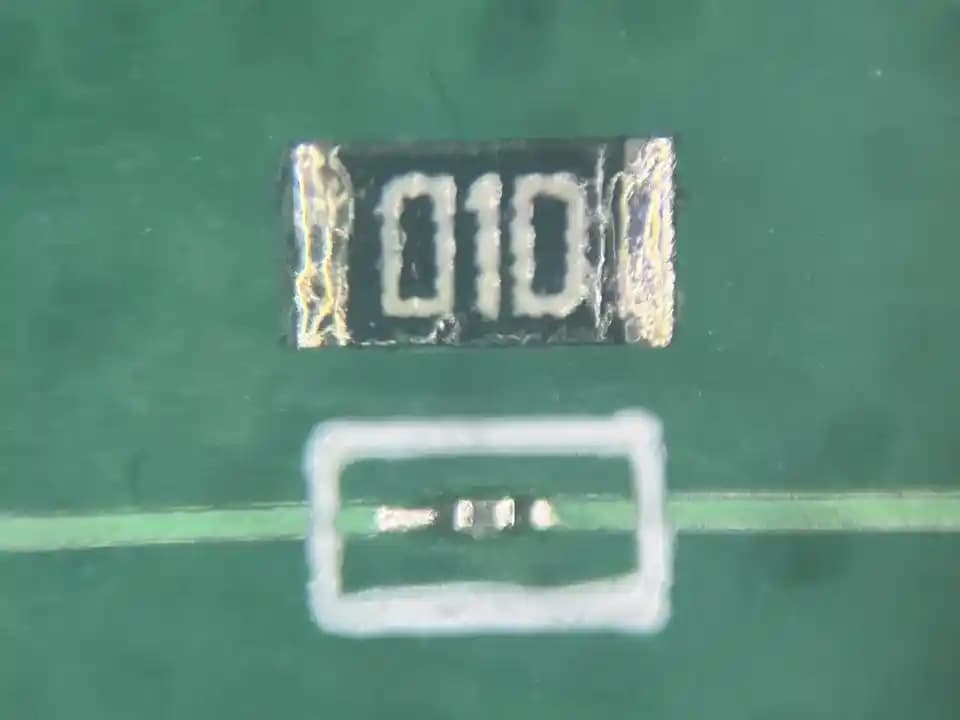

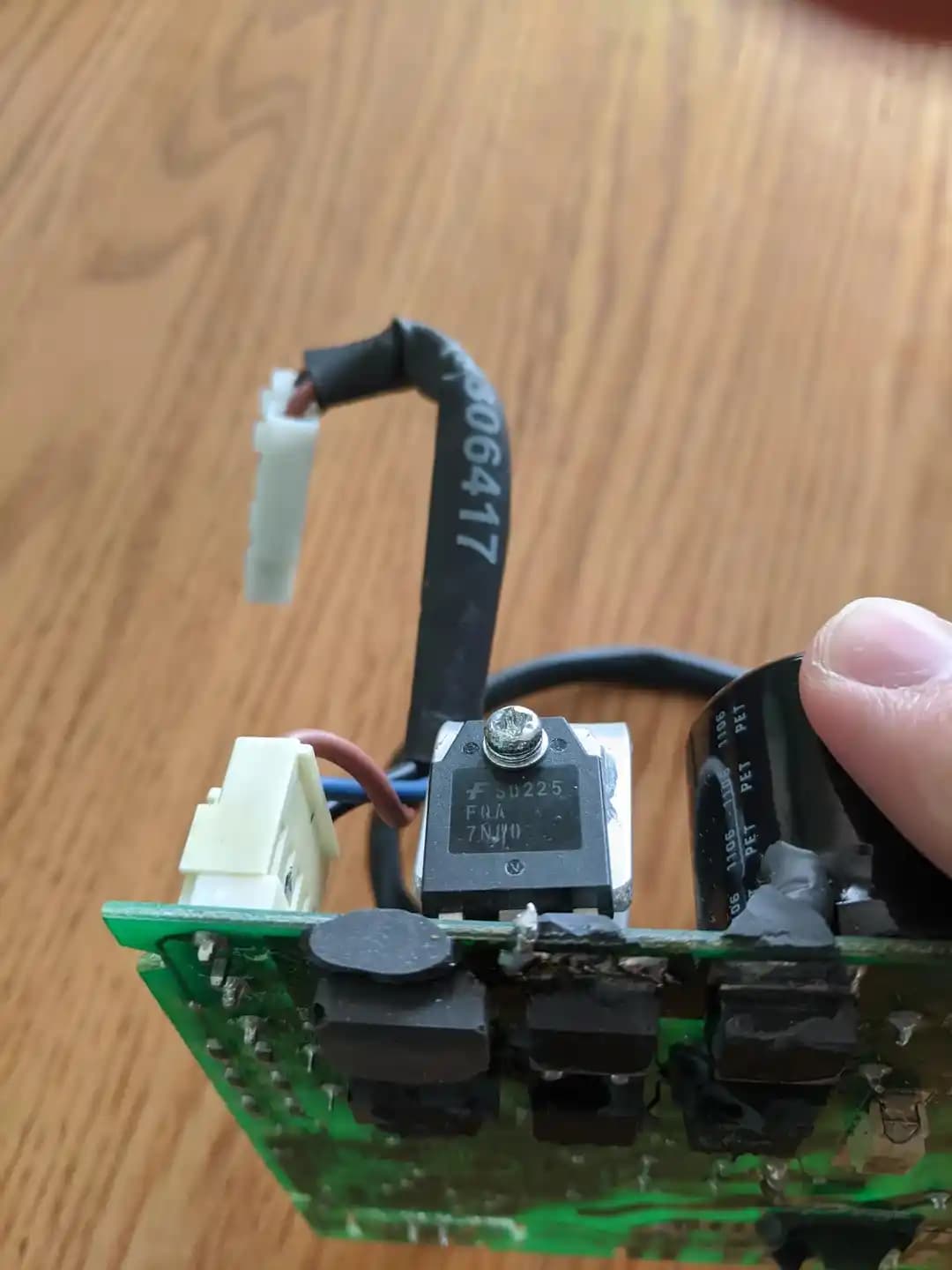

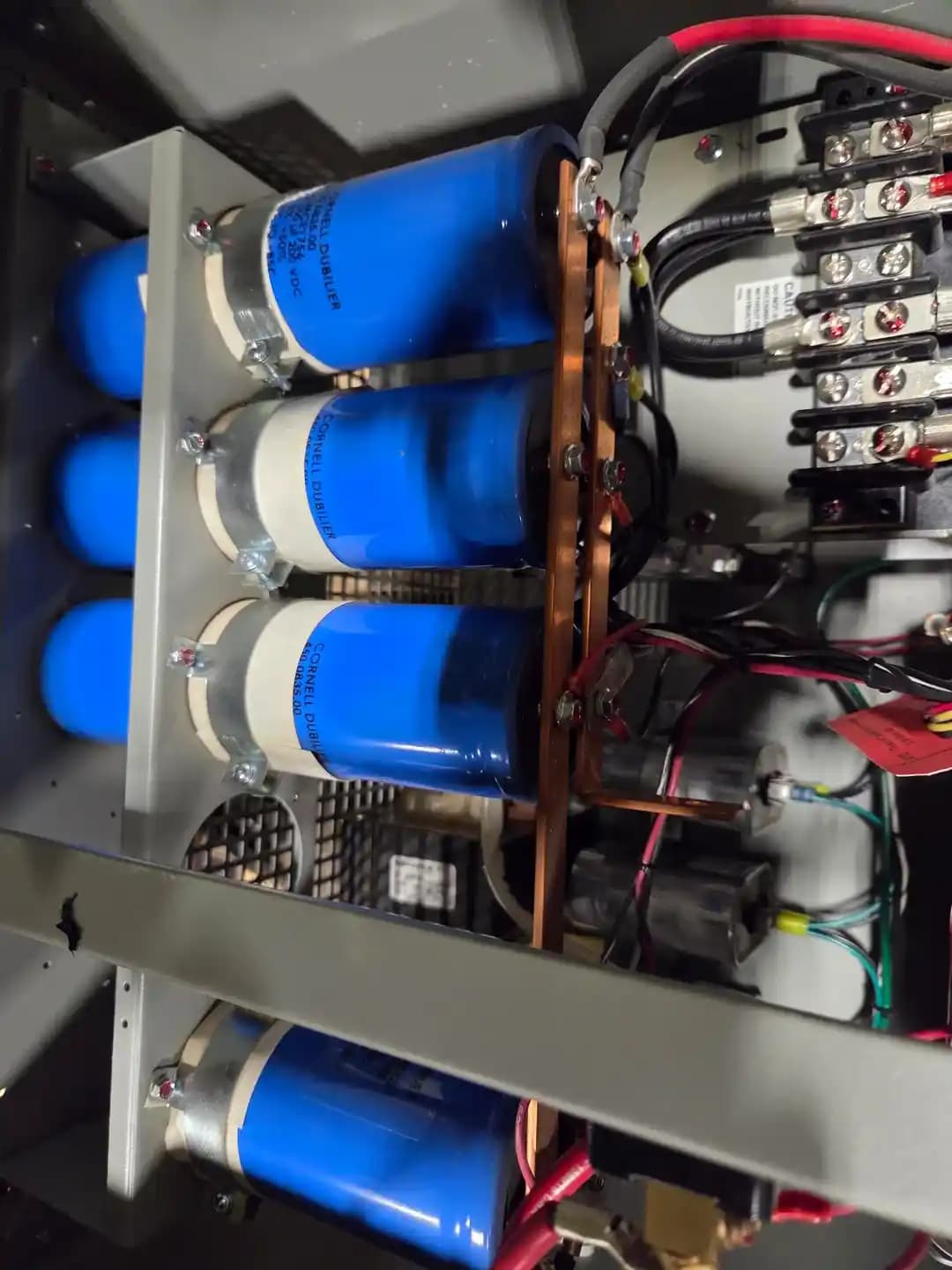

Kapasitör yığma, birden fazla kapasitörün mekanik olarak üst üste konulup, özel lehimleme plakaları (stacking plates) ile birleştirilmesi işlemidir. Bu yöntemle, kapasitörler tek bir bileşen gibi davranarak toplam kapasitans artar ve ESR değeri düşer.

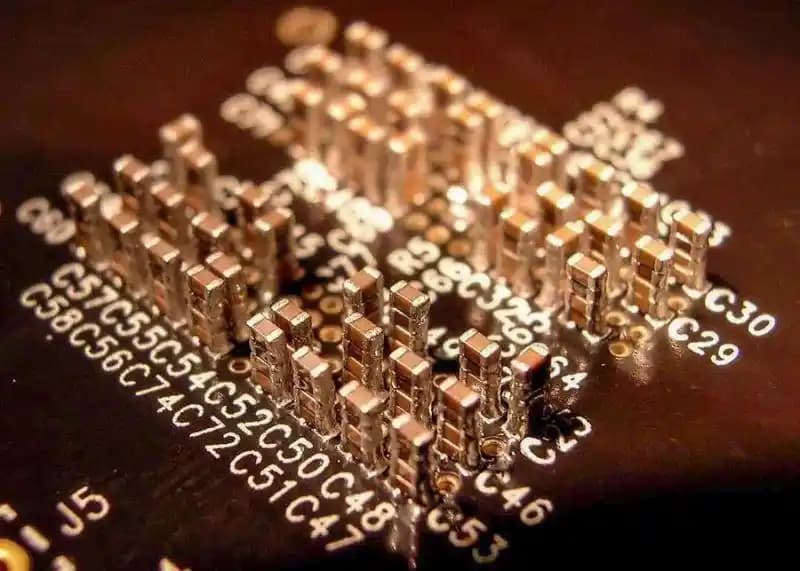

Örneğin, birden fazla küçük kapasitörün yığılması, aynı alan içinde daha yüksek kapasite ve daha düşük ESR sağlar. Bu, özellikle BGA (Ball Grid Array) gibi yoğun paketleme gerektiren entegre devrelerin güç beslemesinde tercih edilir.

Reddit'te paylaşılan örneklerde, kapasitörlerin üst üste dizilimi ve lehimleme plakalarıyla birleştirilmesi görülmektedir. Bu tasarım, devre kartında yer tasarrufu sağlarken, kapasitörlerin filtreleme ve enerji depolama kapasitesini artırır.

Ayrıca Bakınız

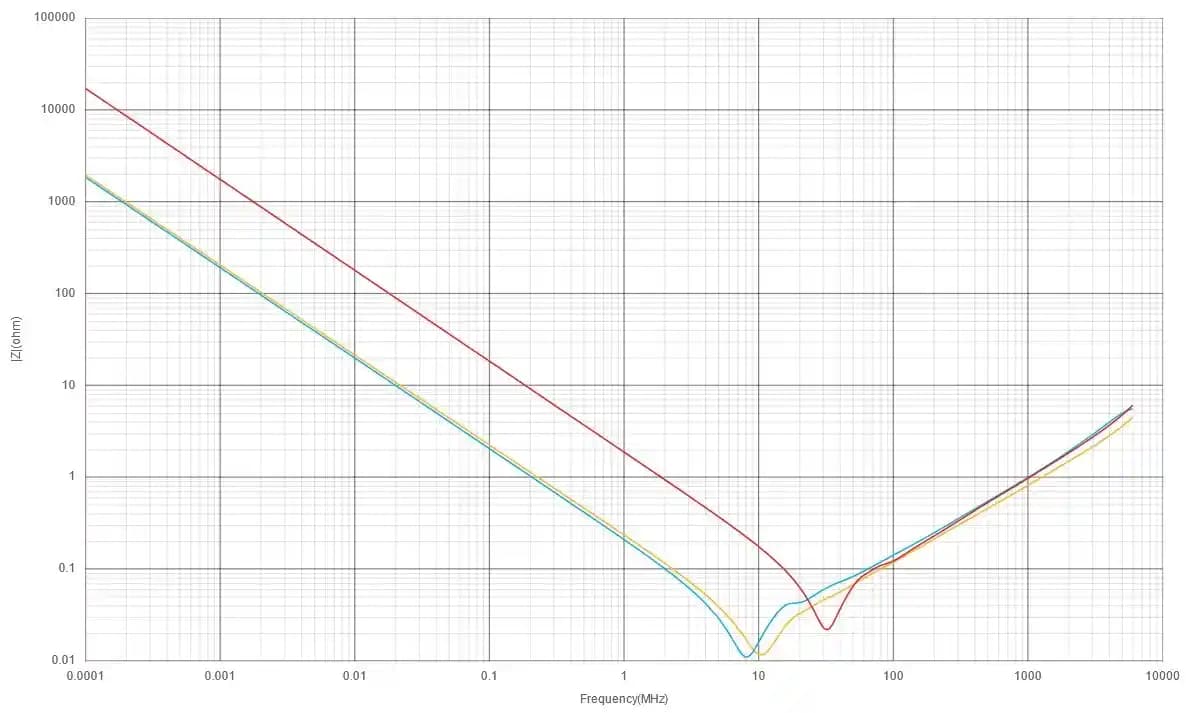

ESR ve ESL İlişkisi

Düşük ESR, kapasitörlerin hızlı enerji depolayıp boşaltabilmesi için önemlidir. Ancak kapasitör yığma yöntemi, ESL (eşdeğer seri endüktans) değerini artırabilir. ESL, kapasitörün yüksek frekanslardaki performansını etkiler ve genellikle kapasitörün fiziksel boyutu ve yapısıyla ilişkilidir.

Yığılmış kapasitörlerde, kapasitörlerin birbirine bağlanma şekli ve montaj yapısı ESL değerini yükseltebilir. Bu nedenle, tasarımcılar ESL değerini minimize etmek için kapasitörlerin yerleşimi ve bağlantı yollarını dikkatle planlamalıdır.

Tasarım Zorlukları ve Dikkat Edilmesi Gerekenler

Mekanik Dayanıklılık: Kapasitörlerin üst üste yığılması, titreşim ve mekanik zorlanmalara karşı hassas olabilir. Bu nedenle, montajda sağlam lehimleme ve destek yapıları gereklidir.

Kapasitör Derating (Kapasite Azalması): Özellikle seramik kapasitörlerde, DC yük altında kapasite azalma (derating) yaşanabilir. Yığma yöntemi, bu etkileri dengelemek için daha fazla kapasite eklenmesini gerektirebilir.

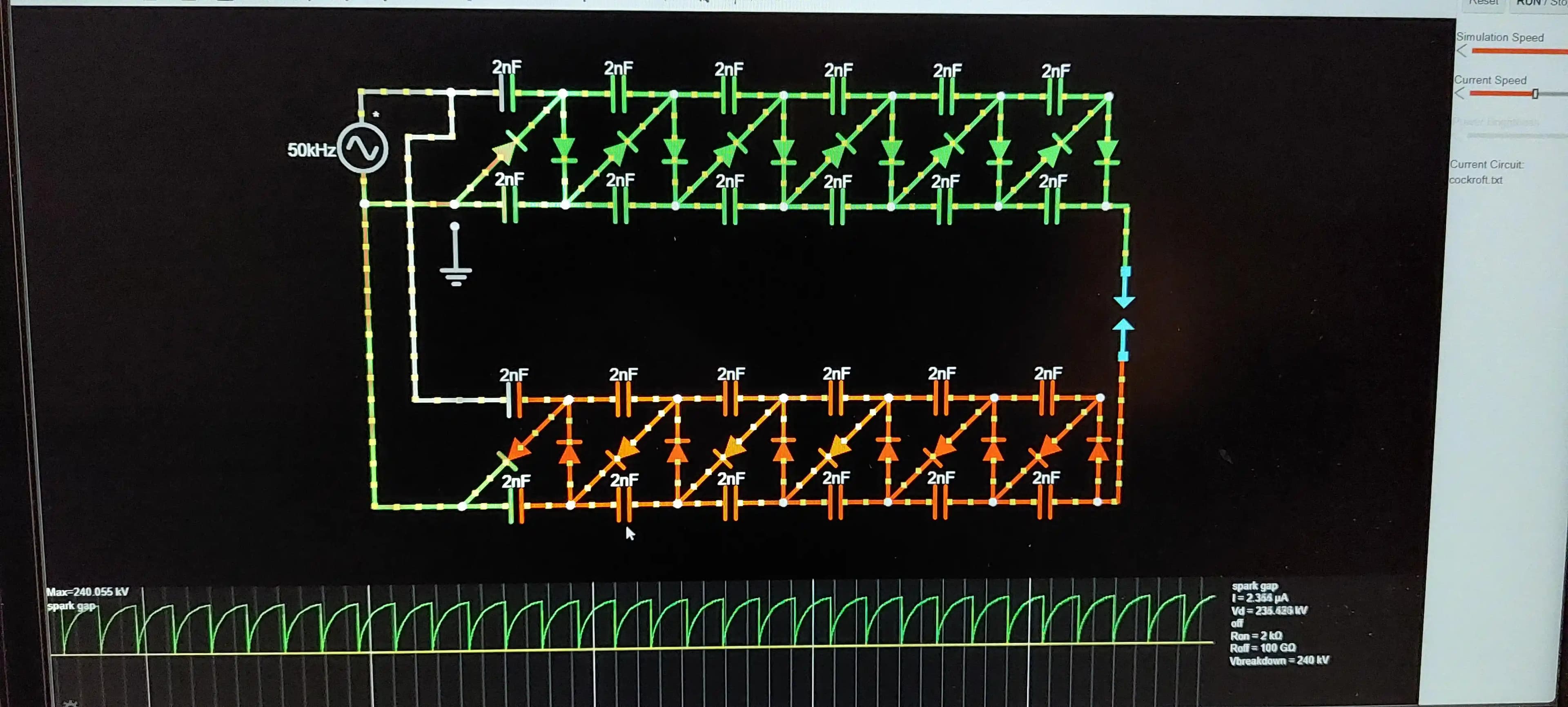

EMC Testleri: Yetersiz bypass kapasitansı, elektromanyetik uyumluluk (EMC) testlerinde başarısızlığa yol açabilir. Kapasitör yığma yöntemi, yeterli bypass sağlamak için kullanılabilir.

Referans Tasarım Uyumu: Tasarımcıların, referans devre şemalarına uygun nominal değerlerde ve uygun kapasitör tiplerinde seçim yapmaları önemlidir.

Sonuç

Kapasitör yığma tekniği, sınırlı alanlarda düşük ESR elde etmek için uygulanabilir ve tasarımda önemli avantajlar sağlar. Ancak, ESL artışı, mekanik dayanıklılık ve kapasitör derating gibi faktörler göz önünde bulundurulmalıdır. Tasarımcıların bu yöntemi kullanırken simülasyon araçları ve deneysel testlerle performansı doğrulamaları önerilir.

"İmpedans (ESL yoluyla) kapasitörlerde paket boyutuyla belirlenir. Bu yüzden, BGA altında sığabilecek en küçük boyutta en yüksek değeri kullanın." – Reddit kullanıcısı

Bu teknik, elektronik devrelerde alan kısıtlamalarının olduğu durumlarda filtreleme ve güç stabilizasyonu için alternatif bir çözüm sunar.